VCS

作者:互联网

一、前言

接触Synopsys 家的VCS工具有一段时间了,在此简单分享下个人的学习笔记。供刚接触到数字前端设计的同学提供一些参考资料。在学校我们经常使用的verilog仿真软件都是quartus和modelsim,但是看一下一些公司的招聘要求,公司里使用的基本都是VCS。所以学习一下对找工作还是有帮助的。

参考资料:1.VCS User Guide 2. VCS labs 3. bilibili搜索VCS,有一些视频教程。

1是官方手册,2是官方给出的几个实验,包涵源码和实验指导文档。1, 2 均可在eetop上找到并下载。

VCS工具的安装是一个很头疼的事情。本人最开始查阅各种博客,花了两天时间才捣鼓好双系统,在Ubuntu上安装完VCS。到后来发现eetop上有人分享安装完各种EDA的Redhat系统,十分方便。有需要的同学可以去下载。 http://bbs.eetop.cn/thread-876507-1-1.html

12月15更新:上面我分享的虚拟机不知道怎么回事就挂了,现在推荐大家用 docker,和虚拟机一样用,放个贝塔的文章链接:

Synopsys全套docker镜像使用指南102 赞同 · 73 评论文章

在linux下使用EDA需要有linux基础,ls,pwd,cd, touch等基本命令需要会用。还有vim编辑器的简单使用,b站上有许多教程。

https://www.bilibili.com/video/BV1ex411x7Em/?spm_id_from=333.788.videocard.0www.bilibili.com/video/BV1ex411x7Em/?spm_id_from=333.788.videocard.0 https://www.bilibili.com/video/BV1Yt411X7mu?from=search&seid=7745608518924210211www.bilibili.com/video/BV1Yt411X7mu?from=search&seid=7745608518924210211第一个链接里的内容,挑前面讲Linux命令的看看即可。

二、VCS介绍

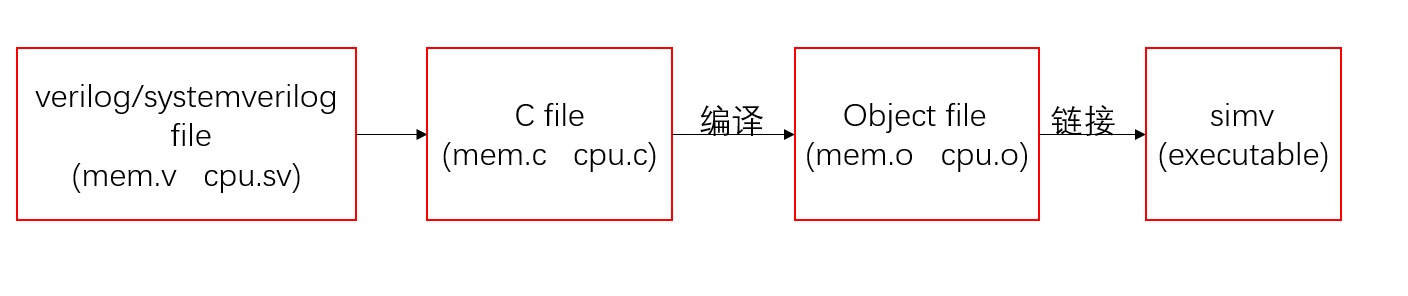

VCS是编译型verilog仿真器,处理verilog的源码过程如下:

图1

图1

VCS先将verilog/systemverilog文件转化为C文件,在linux下编译链接生成可执行文件,在linux下运行simv即可得到仿真结果。

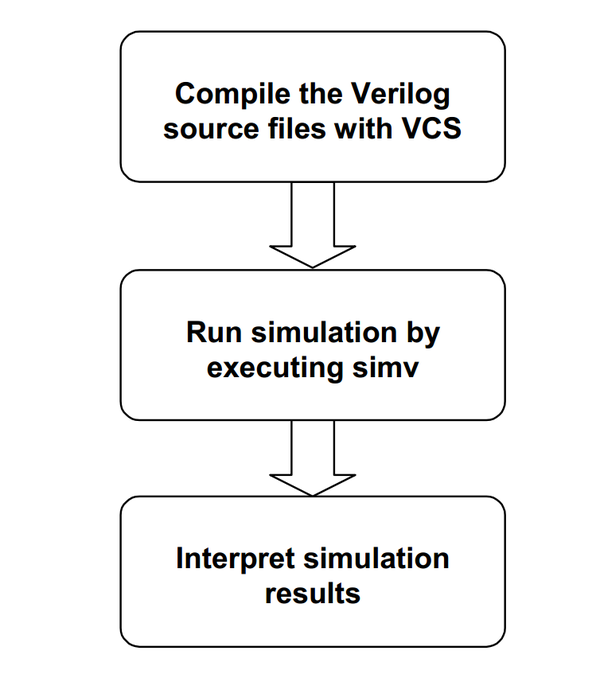

VCS使用步骤,先编译verilog源码,再运行可执行文件:

图2

图2

编译命令的格式:vcs sourcefile [compile_time_option] (编译选项用来控制编译过程)

执行仿真命令格式:./simv [run_time_option]

三、示例

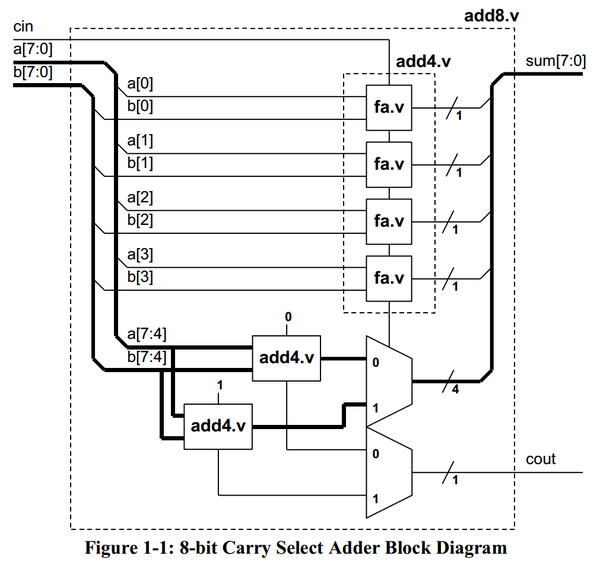

下面使用VCS labs里面lab1的verilog源码做一些示例,电路结构图如下:

图3

图3

此电路为一位加法器 fa.v 组成4位加法器 add4.v,再组成一个8位加法器,使用资源换性能的思路,减小了行波进位加法器的进位延迟。顶层文件为add8.v,testbench为addertb.v。

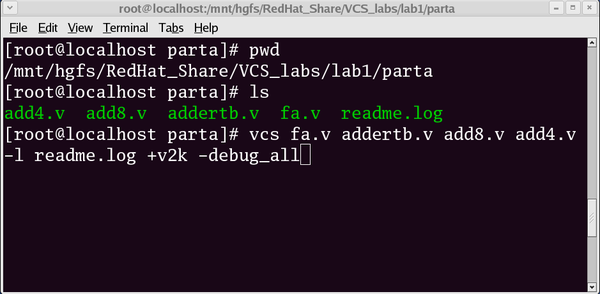

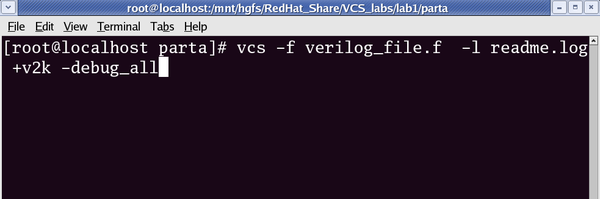

图4

图4

输入上述命令回车即可编译verilog文件,其中-l readme.log 用于将编译产生的信息放在log文件内,+v2k是使VCS兼容verilog 2001以前的标准。-debug_all用于产生debug所需的文件。

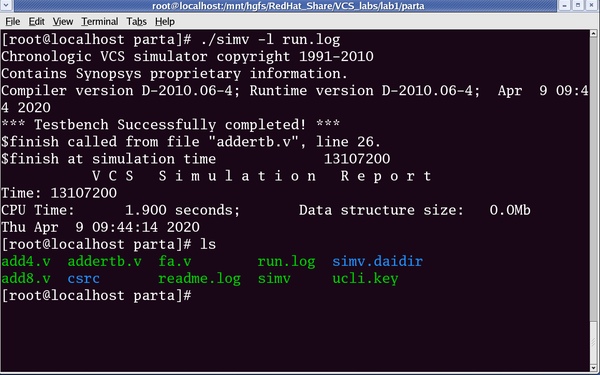

图5

图5

./simv -l run.log 开始仿真,testbench里的$display打印仿真成功的信息,显示在终端上。使用-l run.log 记录终端上产生的信息。

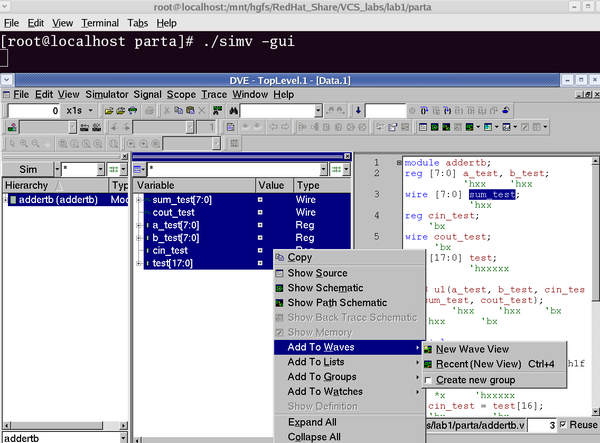

图6

图6

使用./simv -gui 命令打开图形化界面DVE,选中所有信号 --> 右键Add to Waves --> New Wave View

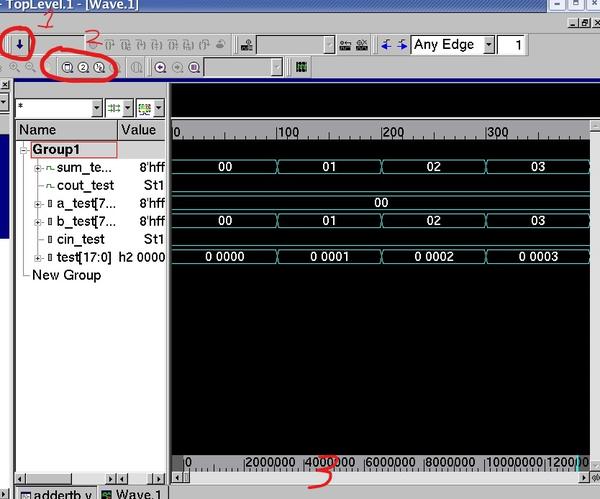

图7

图7

点击1处的小箭头,便有波形出现。使用2处的三个按钮(预览全局、放大和缩小)调整波形。在3处鼠标左键按住不动,左右拖动即可选取一个观察的时间范围。

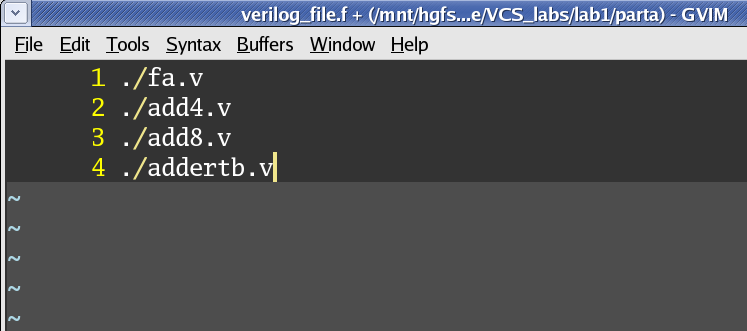

以上已完成VCS基本的使用,下面我们考虑一个更复杂的情形。假设现在顶层模块变得十分复杂,里面包含很多的 .v 文件,我们再像图4那样将所有文件敲在终端上便很麻烦。编译选项-f可以解决这个问题。

图8

图8

在工作目录下新建一个verilog_file.f文件,将所用到的verilog源码以及路径写入文件,并保存退出。

图9

图9

使用-f verilog_file.f 选项,即可将.f文件里的源码全部编译。

以下有其他常用编译选项,注意各个编译选项的顺序,有时出错需要调整。

1) -R 编译后立即运行,即编译完成后立即执行 ./simv

2) -Mupdate 源文件有修改时,只重新编译有改动的.v文件,节约编译时间。

3) -sverilog 打开对Systemverilog的支持,编译Systemverilog文件时使用。

4) -timescale=1ns/1ns 设置仿真精度

5) -o simv_file 编译默认产生的可执行文件为simv,可以使用 -o 更改可执行文件名。

再考虑一种情形,当使用到VCS更多其他功能时,编译选项会变得很长,在终端上一个一个敲变得十分不方便,我们便可以使用makefile来帮助我们编译仿真。在工作目录下新建一个makefile文件

.PHONY:com sim clean

OUTPUT = adder_top

VCS = vcs -sverilog +v2k -timescale=1ns/1ns \

-debug_all \

-o ${OUTPUT} \

-l compile.log \

SIM = ./${OUTPUT} -l run.log

com:

${VCS} -f verilog_file.f

sim:

${SIM}

clean:

rm -rf ./csrc *.daidir *.log simv* *.key

makefile 完成以后,在终端上输入 make com 后回车,相当于在终端中输入以下内容后回车,进行编译。

vcs -sverilog +v2k -timescale=1ns/1ns -debug_all -o adder_top -l compile.log -f verilog_file.f

输入make sim 相当于:

./adder_top -l run.log输入make clean 相当于:

rm -rf ./csrc *.daidir *.log simv* *.key清除一些中间文件。

关于makefile更为详细的介绍,可以去b站观看以下视频,或者阅读《跟我一起写Makefile》

https://www.bilibili.com/video/BV1dW411n7vk?from=search&seid=18160544971512013359www.bilibili.com/video/BV1dW411n7vk?from=search&seid=18160544971512013359四、结束语

以上就是VCS入门的介绍啦,水平有限,若有错误,请批评指教。或私信进一步交流~

发一个VCS lab的文件,上述例子就是用的这个。

链接:https://pan.baidu.com/s/1KCvjeUTzdLhDWXLgD9mlNQ

提取码:jwag

复制这段内容后打开百度网盘手机App,操作更方便哦

VCS入门教程(二)90 赞同 · 11 评论文章

标签:simv,编译,VCS,verilog,com,log 来源: https://www.cnblogs.com/amxiang/p/16688581.html