synthesis建立和保存

作者:互联网

synthesis建立和保存

-

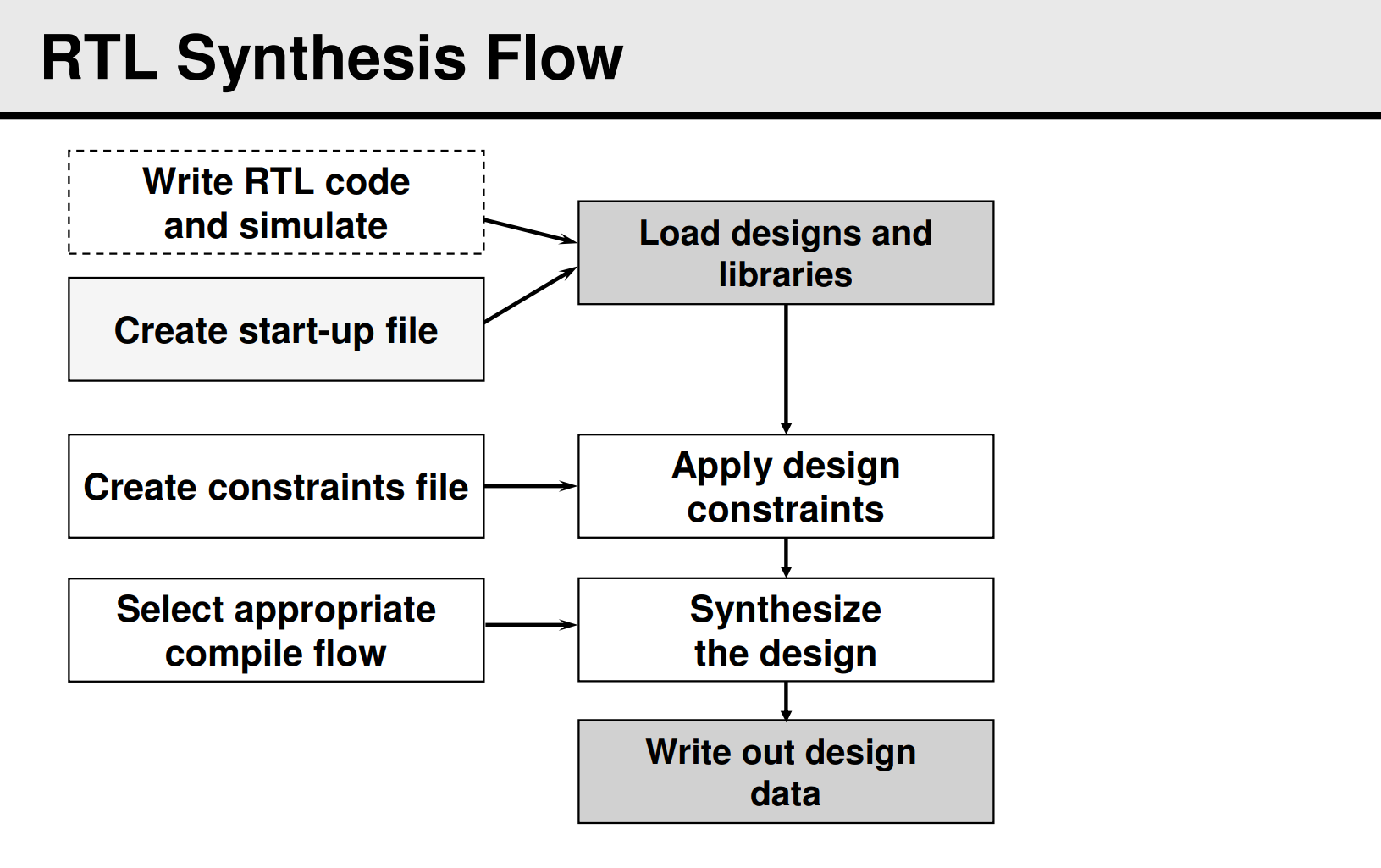

rtl综合过程

-

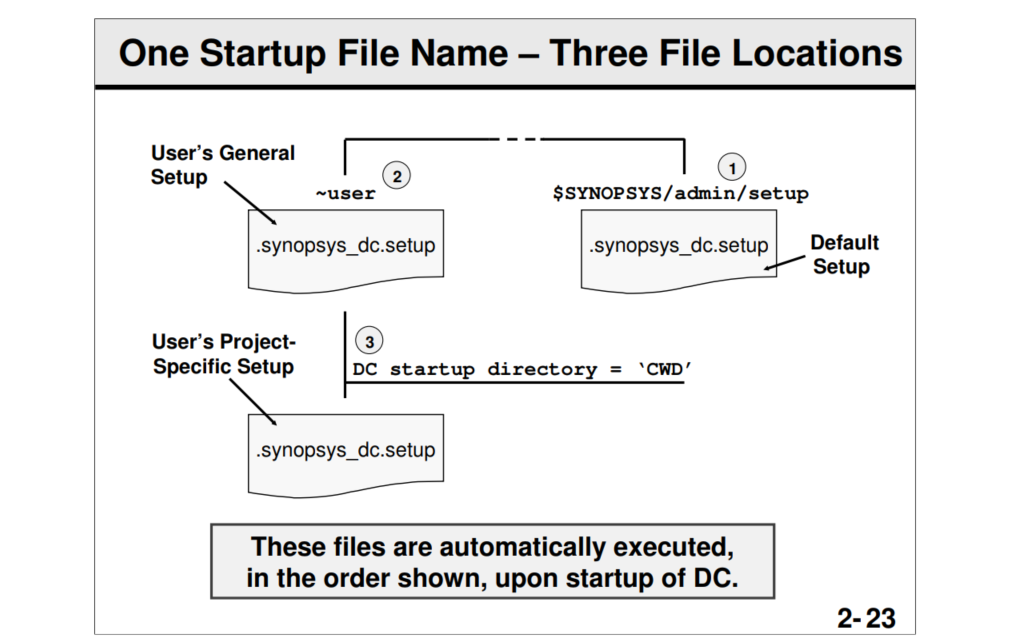

start-up file

启动dc后,会按照下图所示顺序依次执行.synopsys_dc.setup文件。

.synopsys_dc.setup中定义了一些alias命令,source common_setup.tcl和dc_setup.tcl.

启动文件中定义了target_library/link_library/symbol_library/search_path四个变量。

target_library:design要映射到的工艺库(db) link_library:link_library包含target_library,还包含一些IP库等(db) symbol_library:cell的图形化表达库文件(sdb) search_path:design/constraint/library的路径

变量的默认设置

默认指定的库为your_library.db,所以需要在home path .synopsys_dc.setup或CWD .synopsys_dc.setup设定正确的库。

-

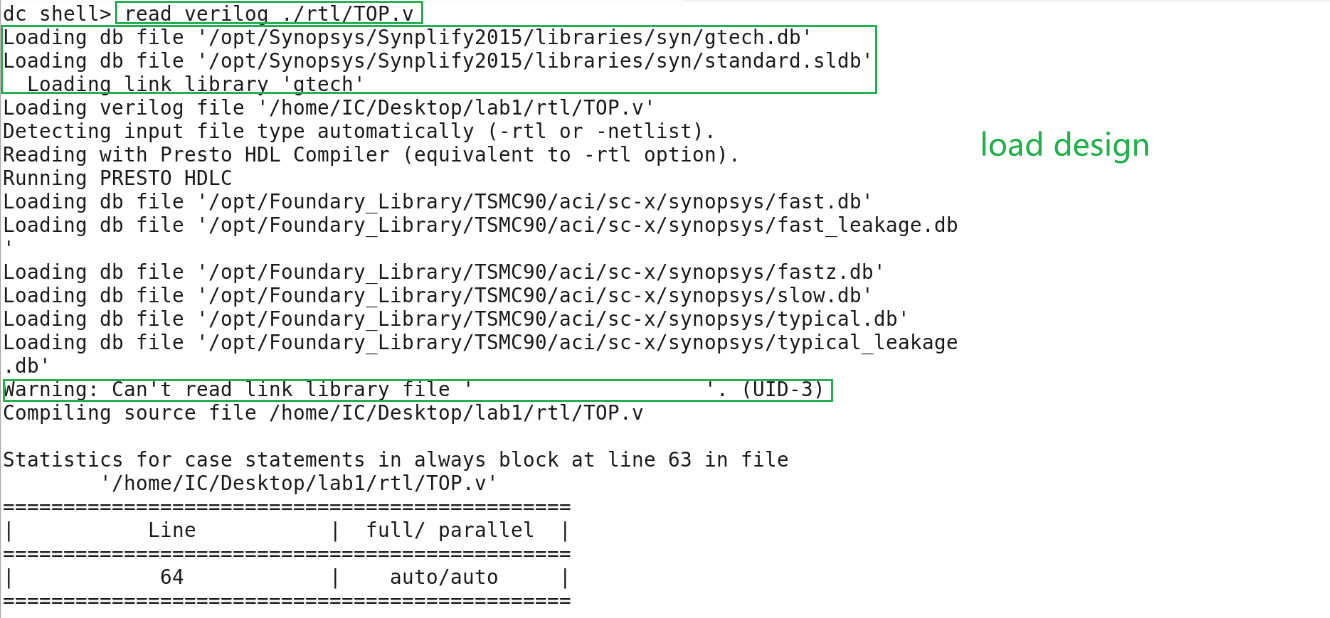

加载设计及库文件

gtech.db和standard.sldb使synopsys提供的默认库,分别包含基本的gtech逻辑单元和design ware IP。读取设计的时候这些库会自动加载。由link_library所指定的库也会在read design时自动加载。

#加载verilog read_verilog design.v #加载VHDL read_vhdl design.vhd

-

synthesis flow

# ====================================================== # # rtl to gtech read_verilog TOP.v current_design TOP link check_design write -f ddc -hier -out gtech/TOP.ddc # ====================================================== # # gtech to netlist source TOP.con check_timing compile -boundary -scan -map high change_names -rule verilog -hier write -f verilog -hier -out netlist/TOP.v write -f ddc -hier -out netlist/TOP.ddc

标签:建立,setup,dc,library,保存,design,TOP,gtech,synthesis 来源: https://www.cnblogs.com/movit/p/14827278.html