CoreSight

作者:互联网

前几日看到新闻,ARM推出CoreSight SoC-600,实现下一代调试与跟踪。何谓下一代?现在你可以丢掉JTAG线了,直接通过WiFi、CAN Bus、Ethernet或USB来进行调试和跟踪你的SoC。听起来是不是前景远大,风光无限?

不过可能很多人对于CoreSight到底是个啥子也不是很清楚,没关系,小编也找了很多资料来学习了一下,或许你看完也能明白了。

根据传统地3W学习方法来探究一下:

WHY:为什么需要

首先从命名上,可以知之一二:就是看看core在干嘛呗!

当然这只是小编的口语。根据ARM的官方,CoreSight主要实现两个功能:Debug和Trace。

对于搞嵌入式的工程师而言并不陌生,也就是对于内核的调试和跟踪功能。

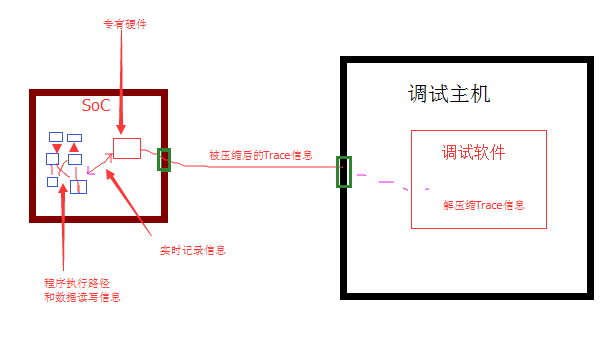

在早期可以通过片外仪器来测量处理器调试过程中的数据和指令流,而后SoC的大范围应用,片内Cache的使用也变得非常广泛。这就使得片外仪器就无法监测了,因此处理器厂商就提供硬件片上的Trace功能,通过专有的硬件非入侵地实时记录程序执行路径和数据读写信息,然后压缩成Trace数据流,通过专用的数据通道和输出端口传输至调试主机(开头提到的600的厉害之处主要就是针对这个位置的创新)。调试主机中的开发工具解压缩这些Trace数据流,恢复程序运行信息后,就可以进行调试和性能分析。

图画的比较挫,可以凑合着看,大概的流程酱紫。当然程序的执行路径和数据读写信息的被专有硬件的实时记录的过程是简化的,这些都是很多部分组成的,分散排放在SoC中。

简言之CoreSight可以帮助用户实现四大功能:SoC的调建,软件调试,系统配置,事后剖析调试。

除了ARM,当然别家也会推出这种Trace技术产品,不过对于我们的读者而言,CoreSight对其的意义应该是最大的吧。(小众的以后可以再扒)

WHAT:是啥

CoreSight你可以将其称之为一种技术,一种硬件,或者叫做一种系统级IP(这个应该是最准确的)。它是ARM公司于2004年推出的一种新的调试体系结构。

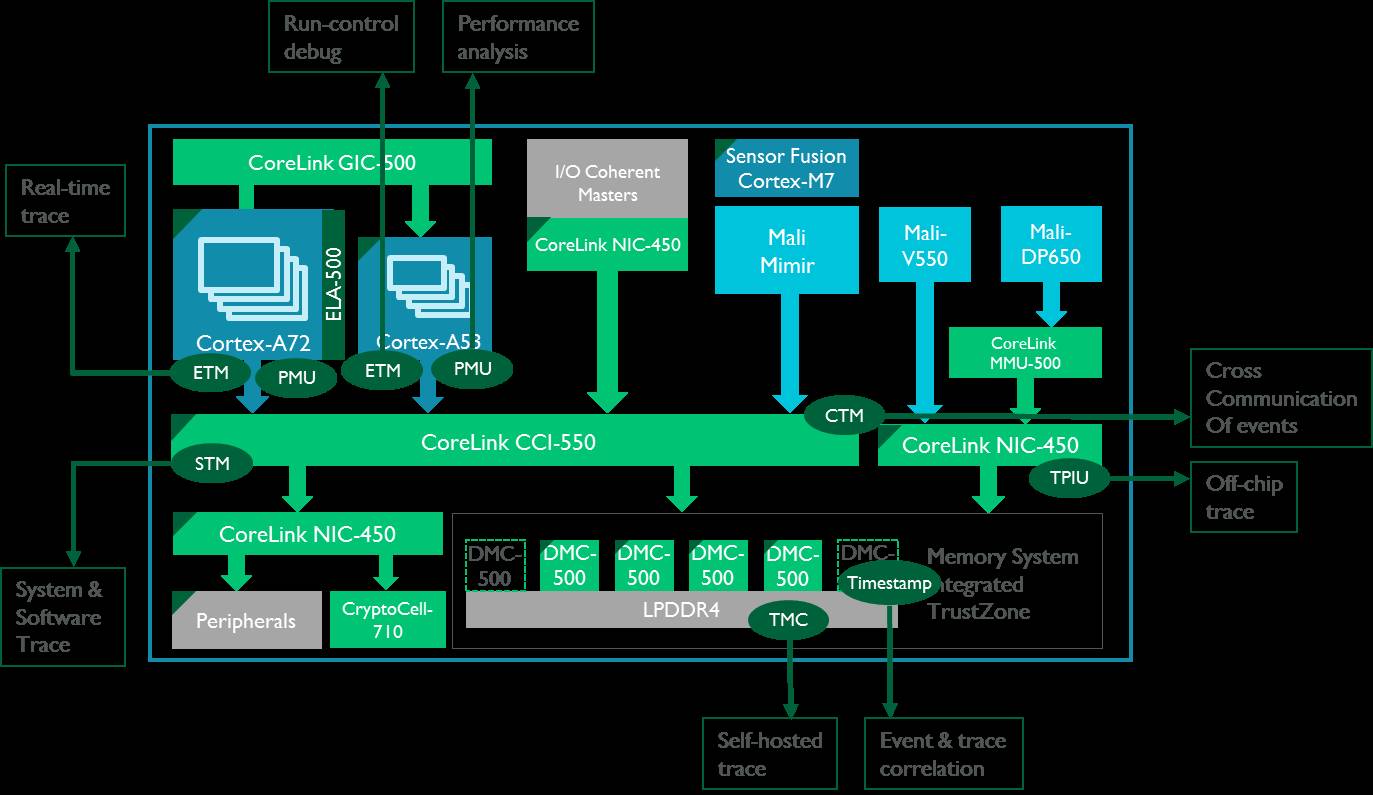

下图中是从ARM官网上down下来的一张关于CoreSight的说明图,图中的ETM,PMU,ETM,CTM,TPIU,STM,TMC以及Timestamp等都属于CoreSight的一部分;各个部分的功能也在上面标明了。

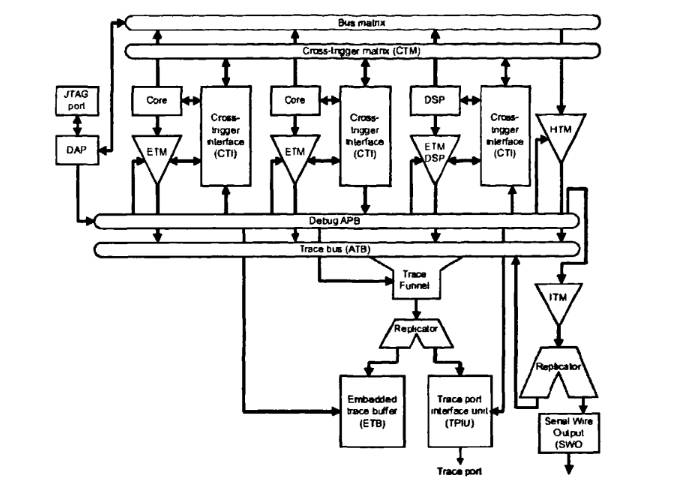

这么多可能看起来有点晕,总结来说CoreSight的调试结构中按照功能可以分为三大部分:Source,Link和Sink。

Source意即源部件,指一些信号或者profile/debug数据的来源,用于产生向ATB(AMBA Trace Bus)发送的跟踪数据,一般是APB总线。

比如STM和ETM都属于Source部分。

STM (System Trace Macrocell):用于获取系统的跟踪信息。

ETM (Embedded Trace Macrocell):用于获取处理器核的跟踪信息。

Sink意即控制访问部件,配置和控制数据流的产生,但是不产生数据流。 指一些可以保持这些从source过来数据的模块。

比如DAP和ECT都属于Sink部分。

DAP(Debug Access Port):可以实时访问AMBA总线上的系统内存,外设寄存器,以及所有调试配置寄存器,而不需挂起系统。

ECT(Embedded Cross Trigger):包括CTI(Cross Trigger Interface)和CTM(Cross Trigger Matrix),为ETM(Embedded Trace Macrocell)提供接口,用于将一个处理器的调试事件传递给另一个处理器。

Link意即汇聚点,芯片上跟踪数据的终点。指用于引导从source到sink过程中的类似于通道作用的模块。

比如TPIU、ETB和SWO都属于汇聚点。

TPIU(Trace Port Interface Unit):将片内各种跟踪数据源获取的信息按照TPIU帧的格式进行组装,然后通过Trace Port传送到片外。

ETB(Embedded Trace Buffer):一个32位的RAM,作为片内跟踪信息缓冲区。

SWO(Serial Wire Output):类似TPIU,但仅输出ITM单元的跟踪信息,只需要一个引脚。

How:DS5

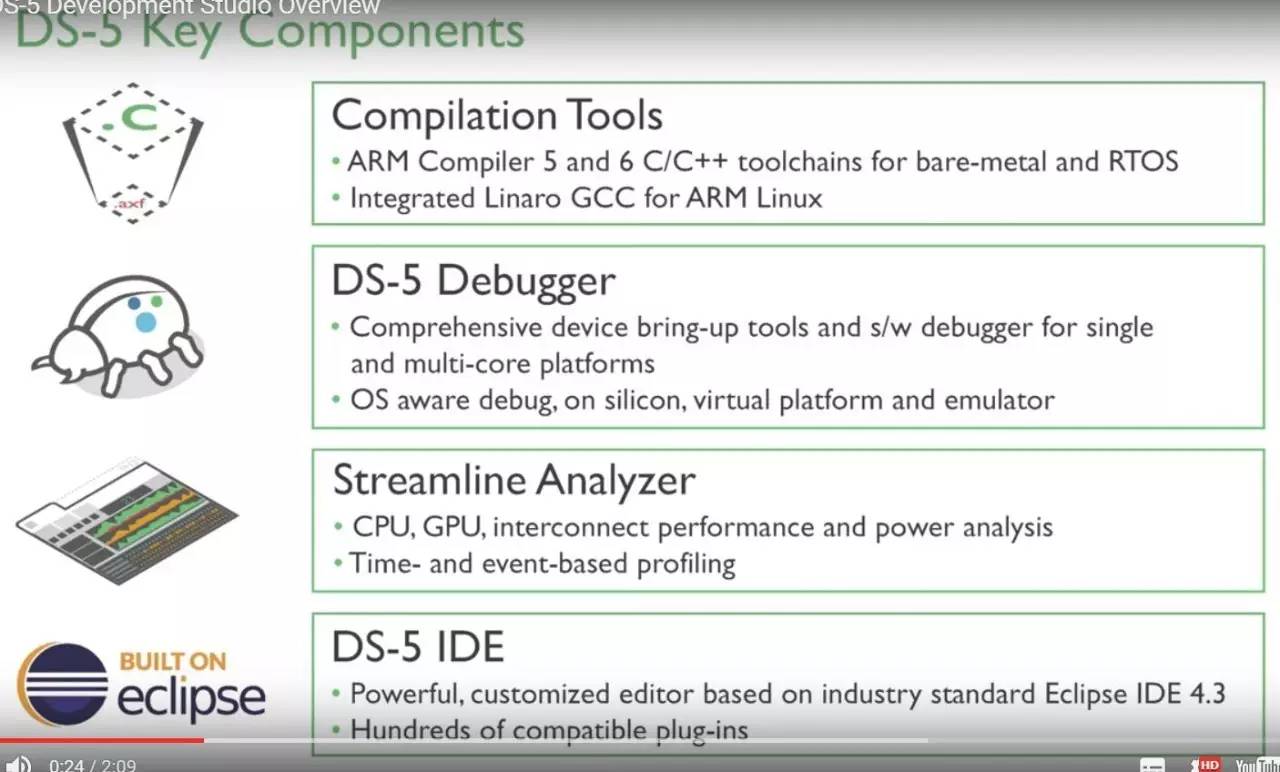

上图是一个典型的CoreSight调试结构,上文中已经提及,在此不在赘述。这里主要说明一下如何在软件上实现How。开发者可以使用ARM DS Development Tools来实现CoreSight的调试和追踪,亦可选择超过25个第三方的开发工具。

其中DS5是目前最新的版本,其中主要包含三个组件,分别是编程工具,调试工具和流水线分析工具。DS-5 调试器兼具集成的微控制器工具的方便性和高生产率以及针对 Linux 的开放源工具的强大功能和灵活性。其基于 Eclipse 的 GUI 简化了管理不同目标连接类型的复杂工作,为在启动加载程序、内核和应用程序级别进行软件调试提供多种不同的方式,同时,其与 GDB 类似的命令行接口为专业的 Linux 用户增添了快速控制和脚本撰写功能。

篇幅受限,下面仅通过跟踪角度来简单讲述DS5的如何使用CoreSight的Trace功能,相信大家可以做到管窥一斑而知全豹。

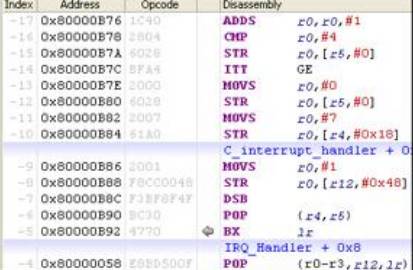

非侵入性跟踪

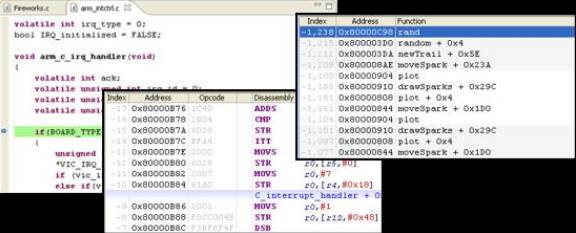

在调试软件时,在许多情况下,错误的负面影响显而易见,但导致出现此类错误的根本原因却远在程序执行之前就已存在。DS-5 调试器所支持的 ARM CoreSight ETM 和 PTM 提供非侵入性程序跟踪,允许开发人员在出现错误时查看说明(以及关联的源代码)。它还使开发人员能够调试对时间敏感的问题,而用传统的侵入性单步技术将很难发现这些问题。DS-5 调试器目前使用 DSTREAM 来捕获 ETB 上的跟踪。还添加了对在此调试和跟踪探针中安装的 4 GB 片外跟踪缓冲区的支持。

灵活的跟踪显示 p<> 跟踪是用于调试和短期性能分析的宝贵工具。但是,只有非常少的开发人员能够应付已执行的机器指令的长长的列表。在 DS-5 中,十分重视以开发人员可以轻松地进行有意义的处理的高级语言来展示这些数据,例如将指令链接到相应的源代码、显示功能级别跟踪分析或者提供图形跟踪显示。

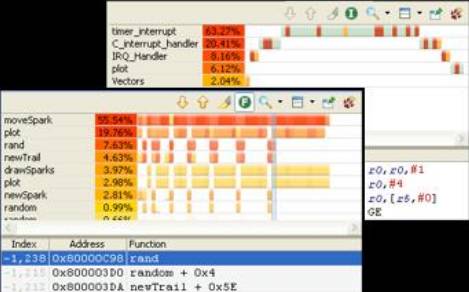

基于跟踪的分析

基于跟踪数据,DS-5 调试器还生成时间表图表,所含信息可帮助开发人员迅速理解其软件在目标上的执行方式以及哪些功能最占用 CPU。通过提供不同的缩放级别,该时间表可基于每个时间单位的指令数显示以其最高分辨率显示热点地图,并且提供按每组指令的典型延迟时间以不同颜色编码的每指令显示。

特别推荐

标签:Trace,ARM,跟踪,DS,调试,CoreSight 来源: https://www.cnblogs.com/amxiang/p/16091919.html