【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十章 PS端RTC中断实验

作者:互联网

原创声明:

本原创教程由芯驿电子科技(上海)有限公司(ALINX)创作,版权归本公司所有,如需转载,需授权并注明出处。

适用于板卡型号:

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

vivado工程目录为“ps_hello/vivado”

vitis工程目录为“ps_rtc/vitis”

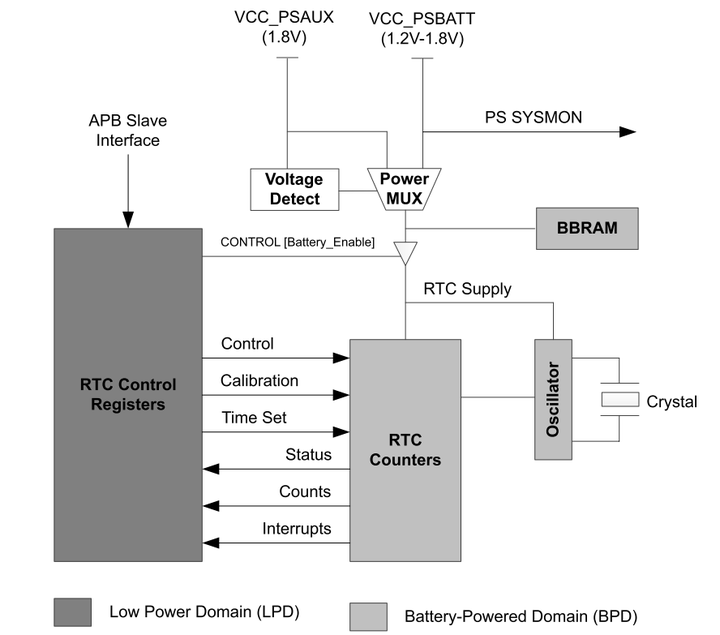

1.RTC介绍

实时时钟(rtc)单元为系统和应用软件提供精确的时间基准。为了满足高精度的需要,实时时钟还包括校准电路,以补偿温度和电压波动。RTC 由 VCC-PSAUX 或 VCC-PSBATT 电源供电。当辅助电源可用时,RTC 使用它保持计数器活动。当辅助电源不可用时,RTC 自动切换到 VCC PSBATT 电源。RTC 功能如下:

1)系统掉电时,该单元自动切换至电池供电,实现时钟的不间断运行

2)支持报警设置和周期中断设置

3)校准电路以确保时间精准

4)三个计数器

时间秒计数器,32 位,可以计数约 136 年

32 KHz 参考时钟计数器,表示 1 秒的计数

用于校准的 4 位分数计数器

RTC控制器结构图

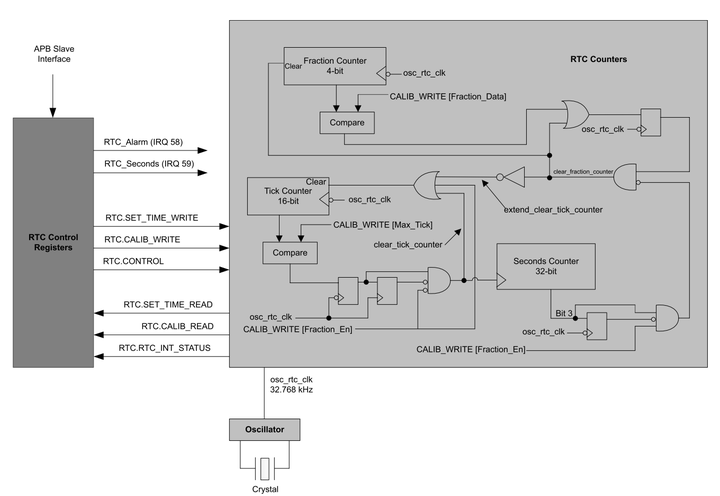

RTC功能图

RTC功能图

2. 中断介绍

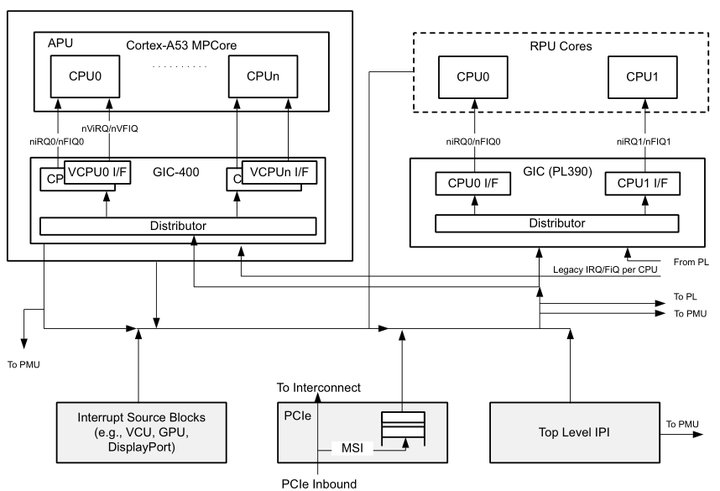

1)ARM cortex-A系列处理器,提供了4个管脚给soc,实现外界中断的传递。分别是:nIRQ、nFIQ、nVIRQ、nVFIQ。arm系统中,会有多个外设,均有可能产生中断发送给core,因此就需要有一个中断控制器来作为中间的桥接,收集soc的所有中断信号,然后仲裁选择合适(高优先级)的中断,再发送给CPU,等待CPU处理。

2)这里中间的桥接,就是arm公司推出的大名鼎鼎的gic(general interrupt controller)。gic其实是一个架构,版本历经了gicv1,gicv2,gicv3,gicv4。

3)Ultrascale+中断框图如下

图中包含两个GIC:

RPU GIC:PL390(arm公司设计的对应GICv1 IP)

APU GIC:GIC-400(arm公司设计的对应GICv2 IP)

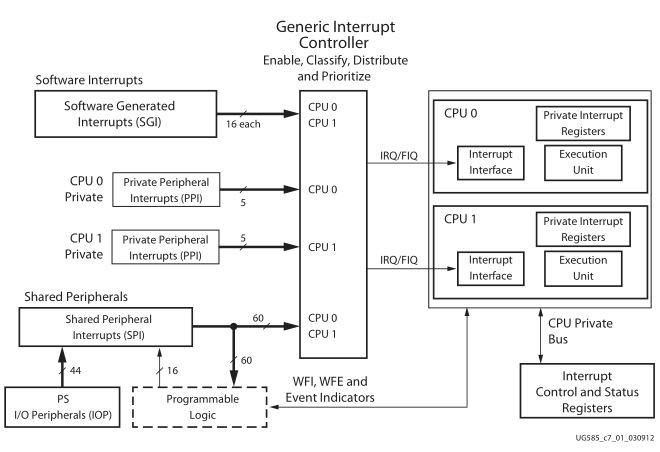

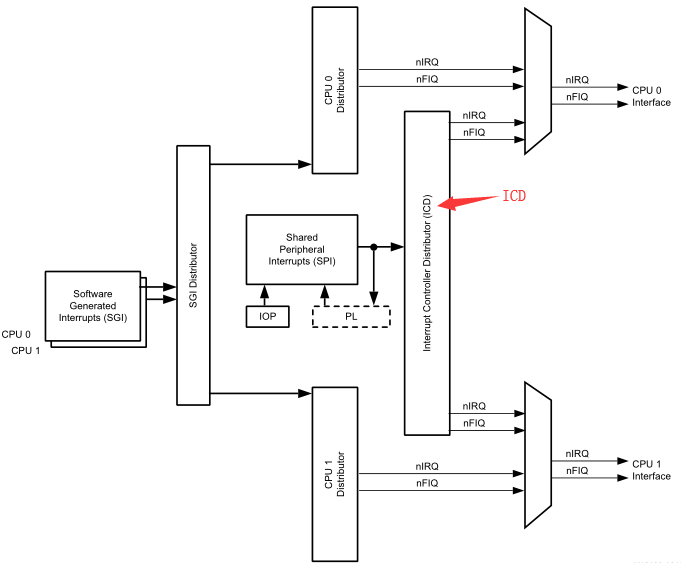

4)RPU GIC,其系统功能框图如下:

从图中可以看到,中断源主要有三种:

PPI:private peripheral interrupt,私有外设中断,该中断来源于外设,只对固定的core有效。

SPI:shared peripheral interrupt,共享外设中断,该中断来源于外设,可以对所有的core有效。

SGI:software-generated interrupt,软中断,软件产生的中断,用于给指定的core发送中断信号

控制器功能框图如下:

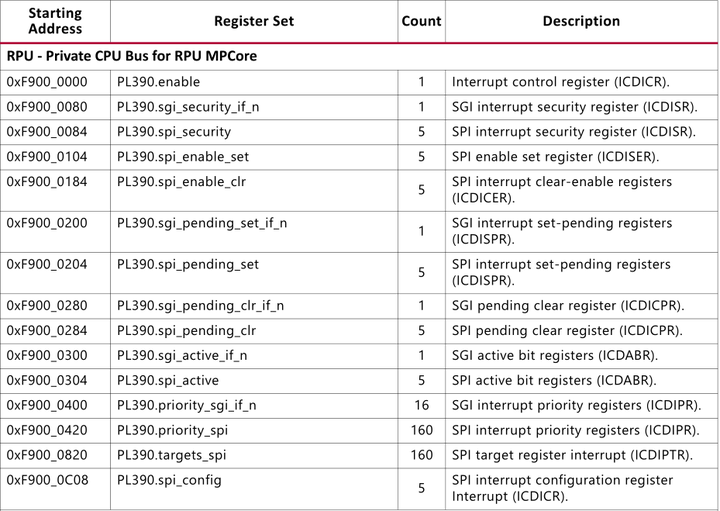

上图中, ICD的控制寄存器主要如下:

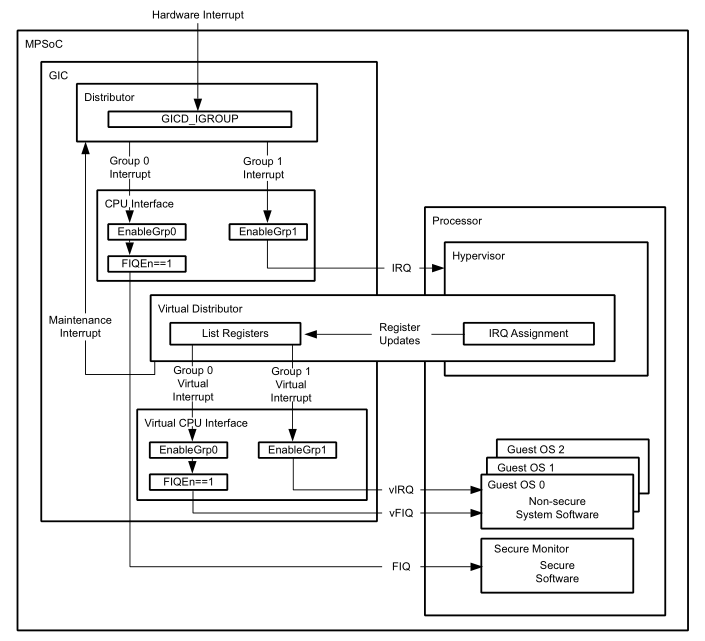

1)APU GIC,功能框图如下

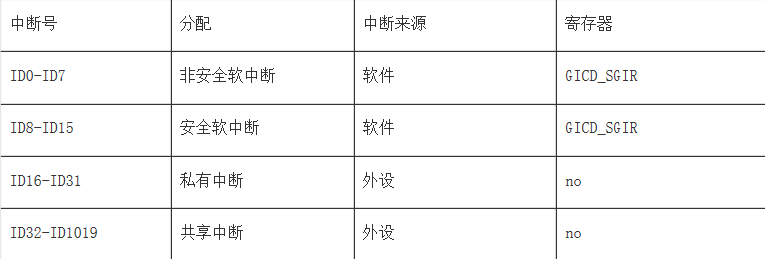

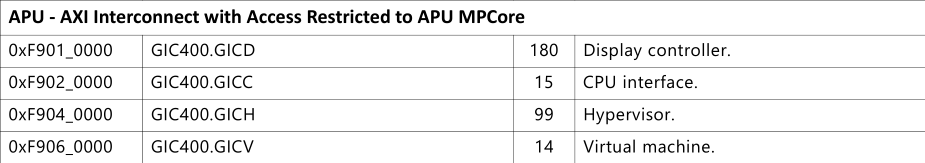

GICv2,将中断分成了group0和group1。使用寄存器GICD_IGROUPRn来对每个中断,设置组。其中group0:安全中断,由nFIQ驱动,group1:非安全中断,由nIRQ驱动。支持最大1020个中断。其中断号分配如下:

GICv2,主要由两部分组成:distributor及cpu interface。

distributor,用来收集所有的中断来源,并且为每个中断源设置中断优先级,中断分组,中断目的core。当有中断产生时,将当前最高优先级中断,发送给对应的cpu interface。其功能有:全局中断使能、每个中断的使能、中断的优先级、中断的分组、中断的目的core、中断触发方式、对于SGI中断,传输中断到指定的core、每个中断的状态管理、提供软件,可以修改中断的pending状态

cpu interface,将GICD发送的中断信息,通过IRQ,FIQ管脚,发送给连接到该cpu接口的core。其功能有:将中断请求发送给cpu、对中断进行认可(acknowledging an interrupt)、中断完成识别(indicating completion of an interrupt)、设置中断优先级屏蔽、定义中断抢占策略、决定当前处于pending状态最高优先级中断

gicv2,定义了自己的一些寄存器,这些寄存器,都是使用memory-mapped的方式去访问的,也就是在soc中,会留有一片空间,给gic。cpu通过访问这部分空间,来对gic进行操作。主要寄存器如下:

这里中断只是作简单介绍,需要详细了解的,请参照xilinx提供的文档:ug1085-zynq-ultrascale-trm.pdf。

软件工程师工作内容

以下为软件工程师负责内容。

3. Vitis程序编写

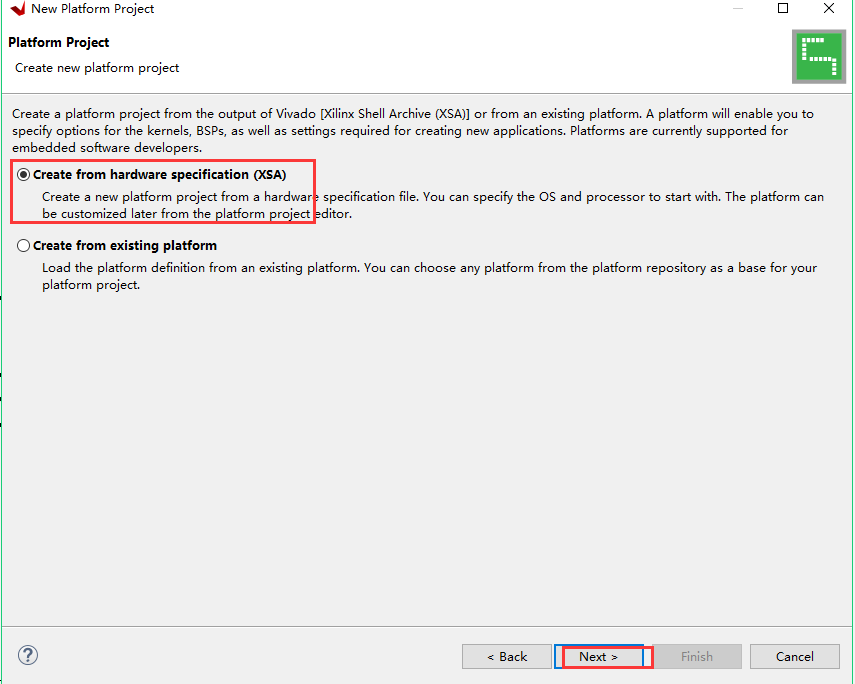

3.1 创建Platform工程

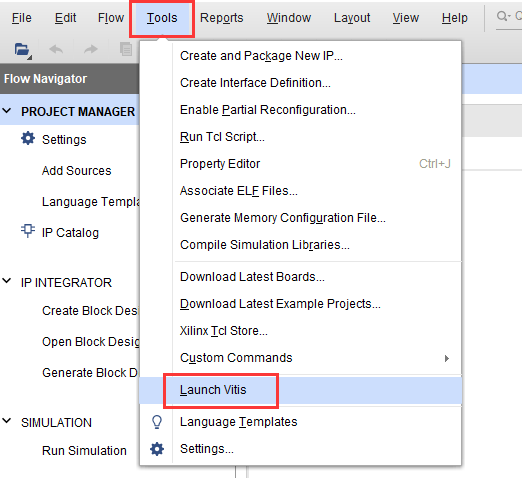

1)点击Tools->Launch Vitis

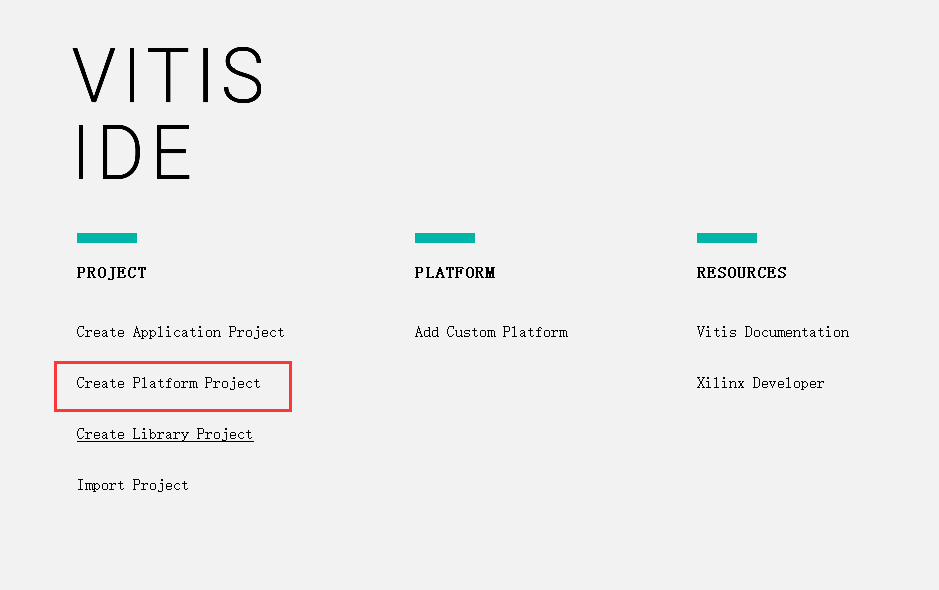

2) 与前面的Hello World实验不同,我们只建立Platform工程

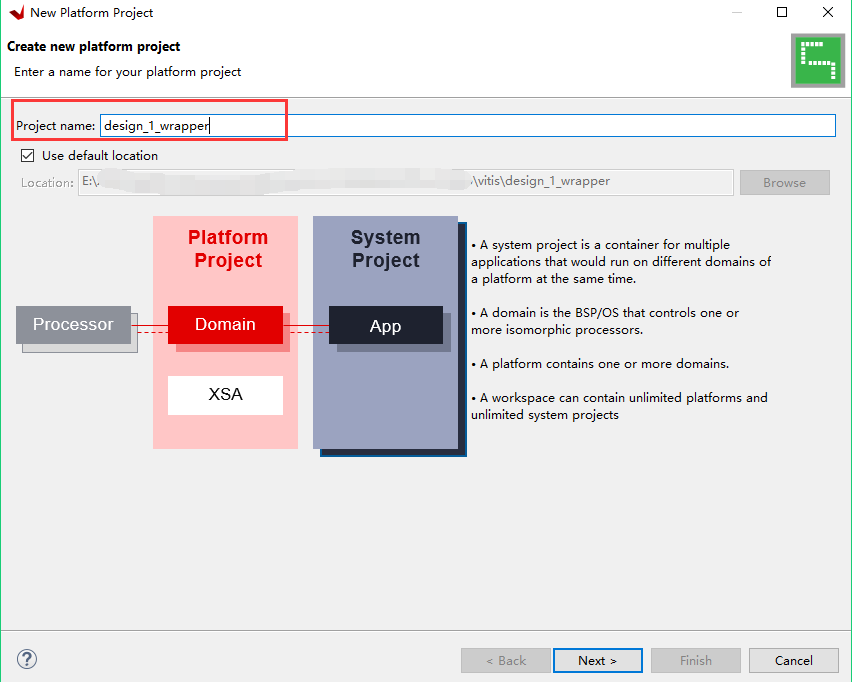

3) 填入工程名字,要与XSA文件的名字一样,点击Next

4) 点击Next

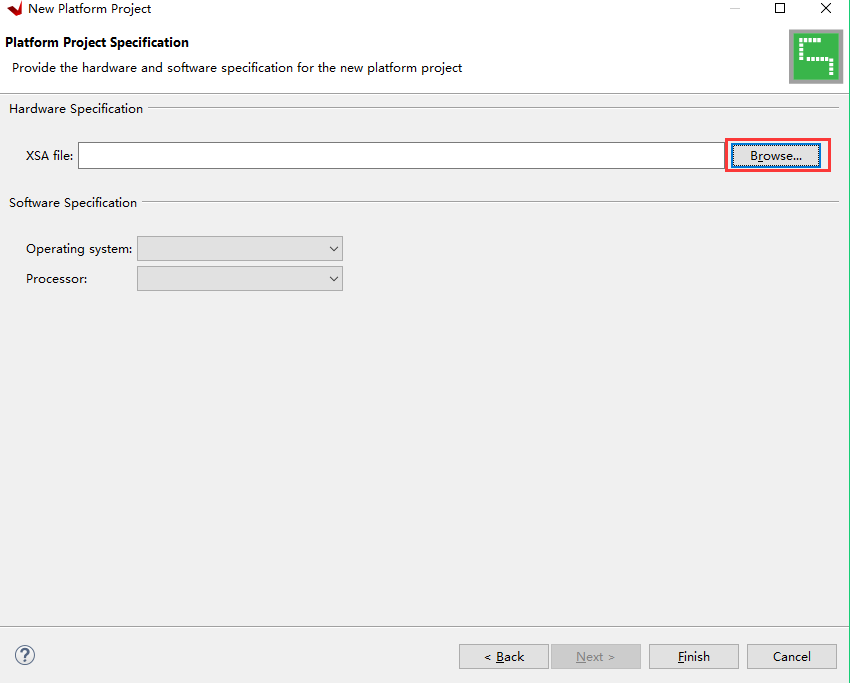

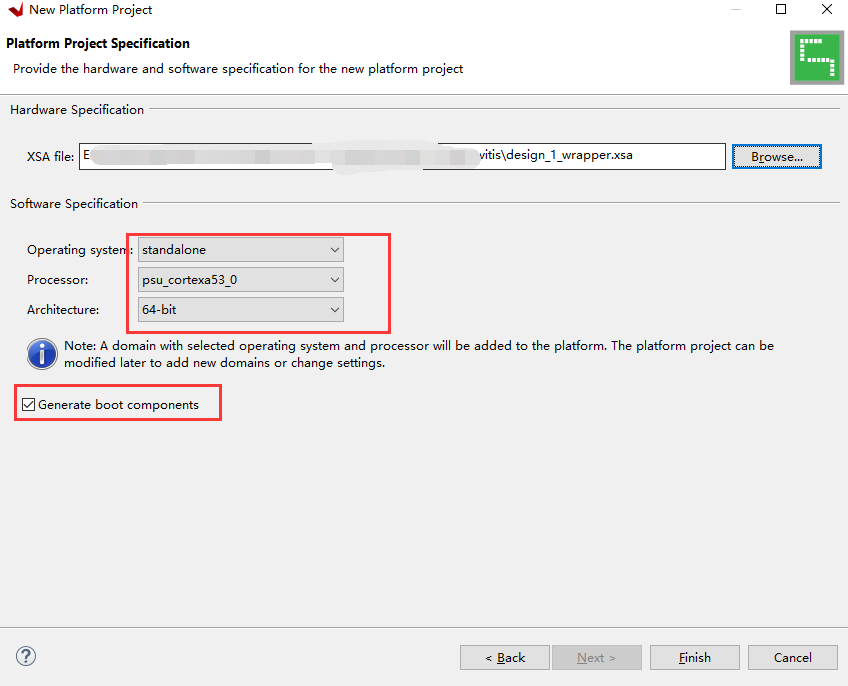

5) 选择XSA文件

保持默认,点击Finish

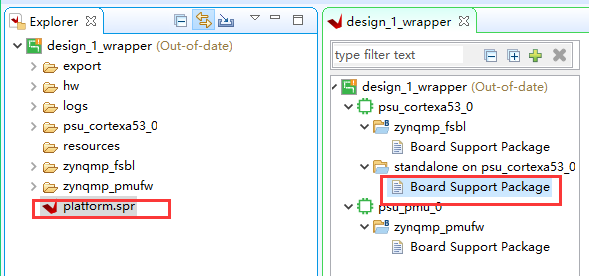

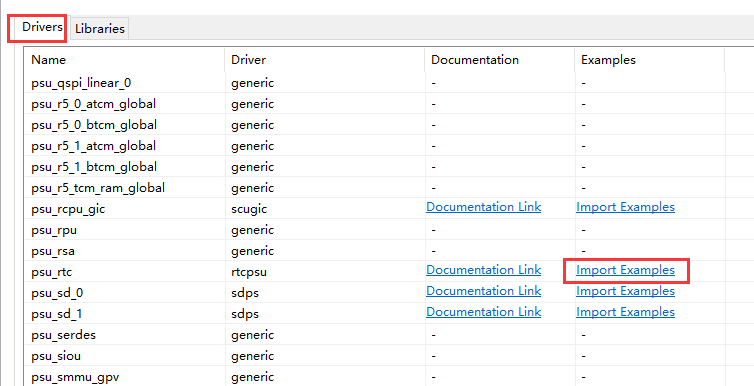

6) 点开platform.spr,并点开BSP

7) 找到RTC驱动,并点击Import Examples

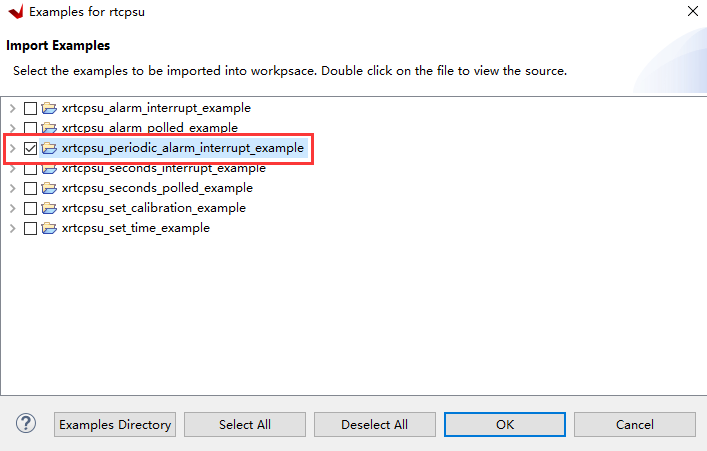

8) 非常幸运,有中断的例子,怎么就知道这个例子就是中断的例子呢?是通过“intr”猜测的,所以,基本功很重要,不然你连找例程都不会。

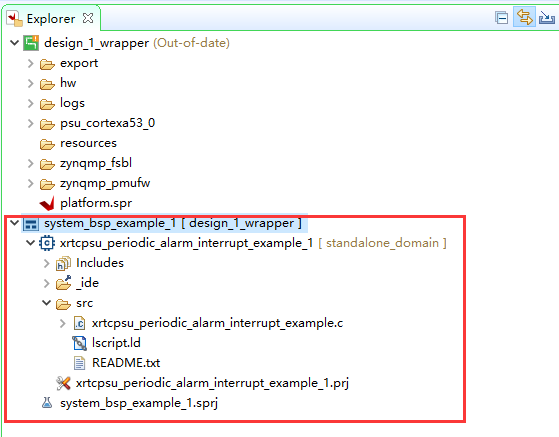

9) 在这里就导入了example工程

下面就是阅读代码,然后修改代码了,当然,可能一下不能完全理解这些代码,只能在以后的应用中去反复练习

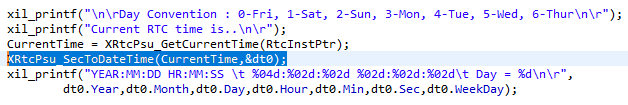

10)通过函数XRtcPsu_GetCurrentTime来获取系统秒计数器值,用函数XRtcPsu_SecToDateTime将计数值转换为我们能看明白的年月日时分秒。

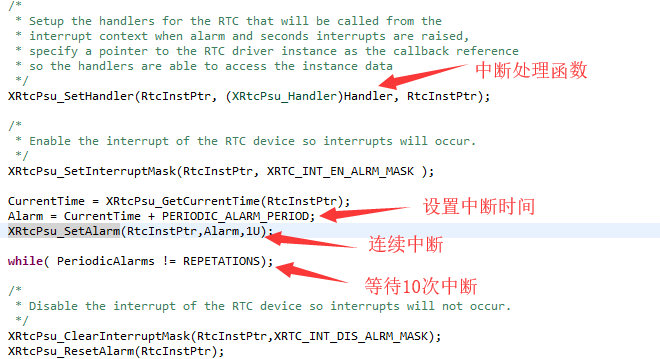

11)设置中断时间,中断时间PERIODIC_ALARM_PERIOD宏定义为2,也就是2秒中断一次

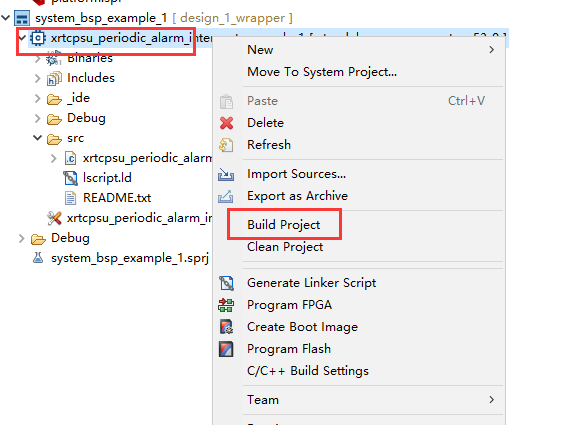

12)Build Project编译

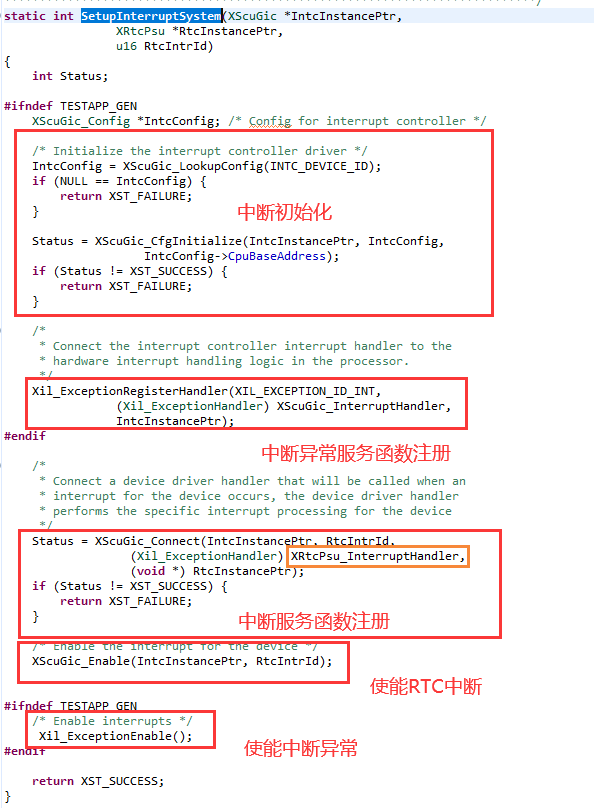

13)了解一下中断控制器的使用,主要分为几个步骤,初始化中断控制器GIC初始化中断异常中断服务函数注册在中断控制器中使能中断使能中断异常。有两步需要注意,在中断控制器中使能中断是要根据中断号使能相应的中断,比如本章介绍的RTC,是在中断控制器GIC中的使能中断,而后面的使能外设中断是指在外设中打开它的中断,正常情况下是不打开的,打开之后就可以产生中断传递到中断控制器GIC。在以后的实验中可以借鉴这种写法。

4. 下载调试

1)打开串口终端;

2)下载调试程序的方法前面教程已经讲解,不再复述;

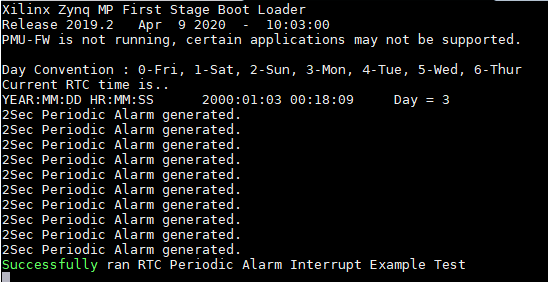

3)和我们预期一样,串口每两秒会看断一次;

5. 实验总结

实验中通过简单的修改Vitis的例程,就完成了RTC,中断的应用,看似简单的操作,但蕴含了丰富的知识,我们需要非常了解RTC的原理、中断的原理,这些基本知识是学习好ZYNQ的必要条件。

标签:MPSOC,控制器,RTC,FPGA,core,中断,GIC,外设 来源: https://www.cnblogs.com/alinx/p/14297797.html