STA,如何计算setup,hold slack以及如何计算电路的最高工作频率

作者:互联网

转载:https://zhuanlan.zhihu.com/p/35189753

介绍STA中最基本的概念以及教你如何计算setup,hold slack以及如何计算电路的最高工作频率。

什么是STA(Staic Timing Analysis)?

- 静态时序分析是用于验证数字设计时序的技术之一

- STA是静态的,因为设计的分析是静态执行的,并且不依赖于在设计的输入所施加的数据值

- STA是对设计的所有时序检查的完整和详尽的验证

为什么要做 STA ?

- 时序分析方法只能验证由simulus执行的设计部分

- 通过时序仿真进行验证只与使用的测试向量一样详尽。

- 为了模拟和验证具有10-100万个门的设计的所有时序条件非常缓慢并且不能完全验证时序。

所以,STA提供了更快,更简单的方法来检查和分析设计中的所有时序路径,以防止任何时序违规。

Dynamic Timing Analysis (DTA) :

- 动态时序分析需要全面的输入向量来检查设计中的时序路径

- 它确定给定输入向量集合的电路的完整行为

- 动态仿真可以验证设计的功能以及时序要求

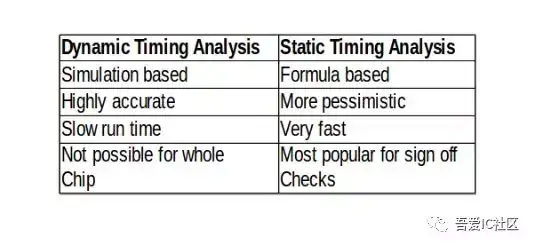

动态时序分析和静态时序分析的区别如下图一所示。

图1 DTA和STA的对比

举个例子,如果我们有100个输入,那么我们需要2的100次方次才能遍历完成整个分析。与静态分析相比,分析量简直是天文数字。

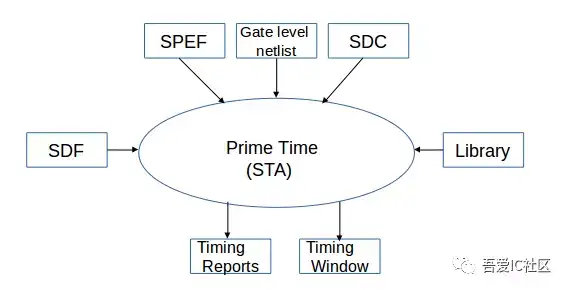

图2 静态时序分析的输入和输出文件

静态时序分析中的一些专业术语:

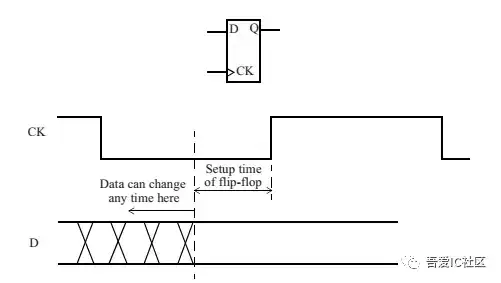

- Setup Time : 在时钟有效沿之前,输入数据必须保持稳定的最小时间,称之为建立时间。

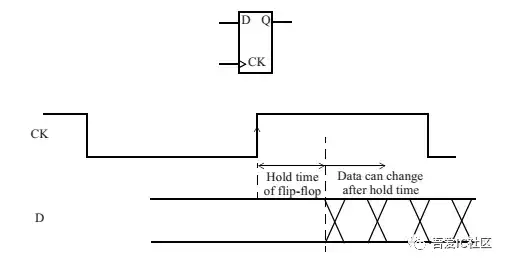

- Hold Time : 在时钟的有效沿之后,输入数据必须保持稳定的最小时间,称之为保持时间。

图3 setup time 和hold time

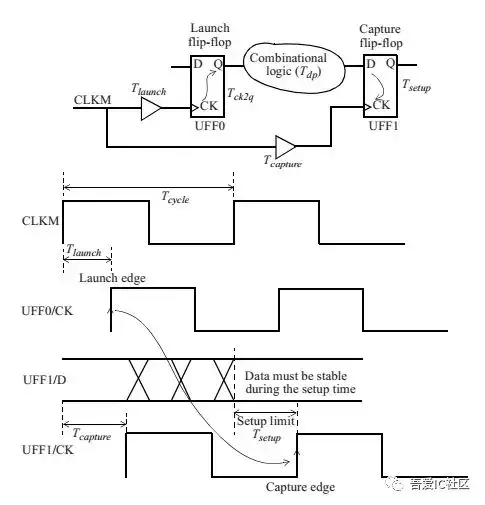

Launch 和Capture edge :

·

- Launch edge是指时钟通过触发器来发射数据的沿edge

- Capture edge是指时钟通过触发器捕获数据的沿edge

Setup timing checks:

setup检查确保数据在时钟的有效沿之前在触发器的输入端可用。

在时钟的有效边沿到达触发器之前,数据应该稳定一段时间,即触发器的建立时间,以便将数据可靠地捕获到触发器中。

setup检查可确保从前一时钟周期启动的数据,在一个周期后能够正确捕获。

图 4 setup检查波形图

Setup 万能套用公式:

[Tlaunch + Tck2q + Tdp] <= [Tcapture + TCLK – Tsetup]

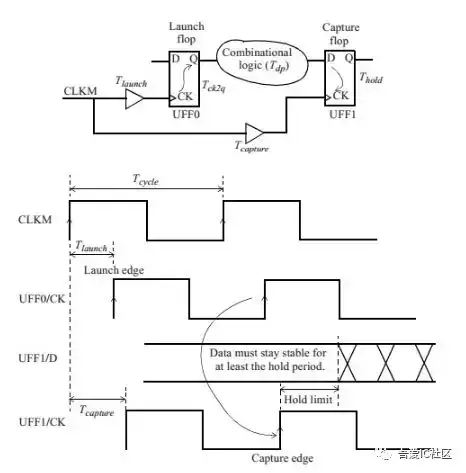

Hold timing checks :

hold检查是确保时钟有效沿来临之后的一段时间内,数据仍然保持稳定,从而确保capture时不至于采集到不稳定或者错误的数据。

图 5 hold 检查波形图

Hold 万能套用公式:

[Tlaunch + Tck2q + Tdp] >= [Tcapture + Thold]

setup和hold的检查机制,也可以阅读之前推送的文章。

深入浅出讲透set_multicycle_path,从此彻底掌握它

Slack(裕量) :

Slack是指数据需要达到时间和实际达到时间之差。

Data Arrival Time : 数据在datapath上传输的时间

Data Required Time : 时钟在clock path上传输的时间

Setup Slack = Data Required Time – Data Arrival Time

Hold Slack = Data Arrival Time – Data Required Time

有了setup和hold概念和计算公式后,很容易就能知道如何去fix setup and hold violation。这个很简单,大家自己多多总结。之前推送的文章数字芯片设计实现中修复setup违例的方法汇总 系统全面介绍过修复setup violation的方法,各位可以前往复习下。

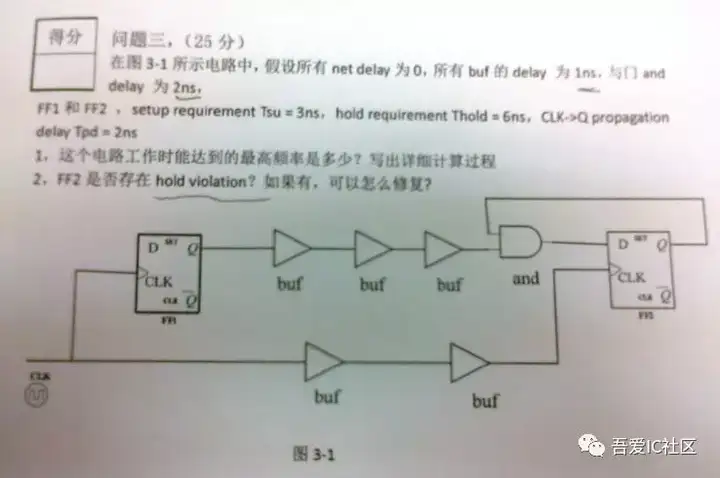

介绍这些基本概念后,我们来个实战。下面这道题是某公司应届生校园招聘的笔试题目,大家做做看。计算电路最高工作频率的面试题数不胜数,几乎一大半的公司都会考这种题。目的是考察应聘者是否熟悉setup,hold检查的方式,是否具备基本的时序分析能力。这道题如果你还不会做或者会做错,请给自己敲个警钟。其实这道题还算简单的,如果存在多条路径到FF2的情况,你是否也能正确算出电路的最高工作频率呢?反正原理是一样的。

图6 电路最高工作频率思考题

标签:STA,setup,时序,Time,hold,时钟 来源: https://www.cnblogs.com/will-w/p/15097527.html